<aside> 💡 “운영체제 : 아주 쉬운 세가지 이야기”를 읽으면서 핵심 내용을 정리하였습니다. 이화여대 반효경 교수님의 운영체제 강의를 듣고 복습 차원에서 책 한권을 완독해보고자 합니다. 잘못된 정보가 있다면 댓글 남겨주시면 감사하겠습니다!

</aside>

페이징을 잘못 구현하면 큰 성능 저하가 올 수 있는데 이유는 아래와 같다

페이징의 한계를 해결하기 위해 하드웨어의 도움을 받는다. 변환 색인 버퍼(translation-lookaside buffer, TLB)는 MMU의 일부로서 자주 참조되는 가상 주소의 변환 정보를 저장하는 하드웨어 캐시이다. 주소 변환 캐시(address-translation cache)라고도 부른다. 가상 메모리 참조시, 하드웨어는 먼저 TLB를 확인하게 된다.

//하드웨어가 관리하는 TLB

VPN = (VirtualAddress & VPN_MASK) >> SHIFT

(Success, TlbEntry) = TLB_Lookup(VPN)

if (Success == True)// TLB HIT

if (CanAccess(TlbEntry.ProtectBits) == True)

Offset = VirtualAddress & OFFSET_MASK

PhysAddr = (TlbEntry.PFN << SHIFT) | Offset

AccessMemory(PhysAddr)

else

RaiseException(PROTECTION_FAULT)

else// TLB MISS

PTEAddr = PTBR + (VPN * sizeof(PTE))

PTE = AccessMemory(PTEAddr)

if (PTE.Valid == False)

RaiseException(SEGMENTATION_FAULT)

else if (CanAccess(PTE.ProtectBits) == False)

RaiseException(PROTECTION_FAULT)

else

TLB_Insert(VPN, PTE.PFN, PTE.ProtectBits)

RetryInstruction()

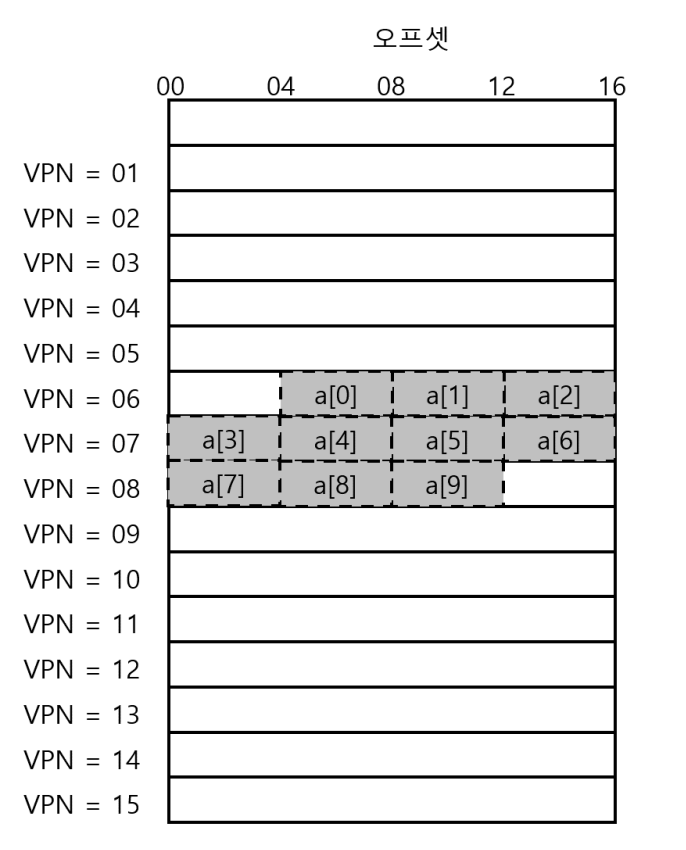

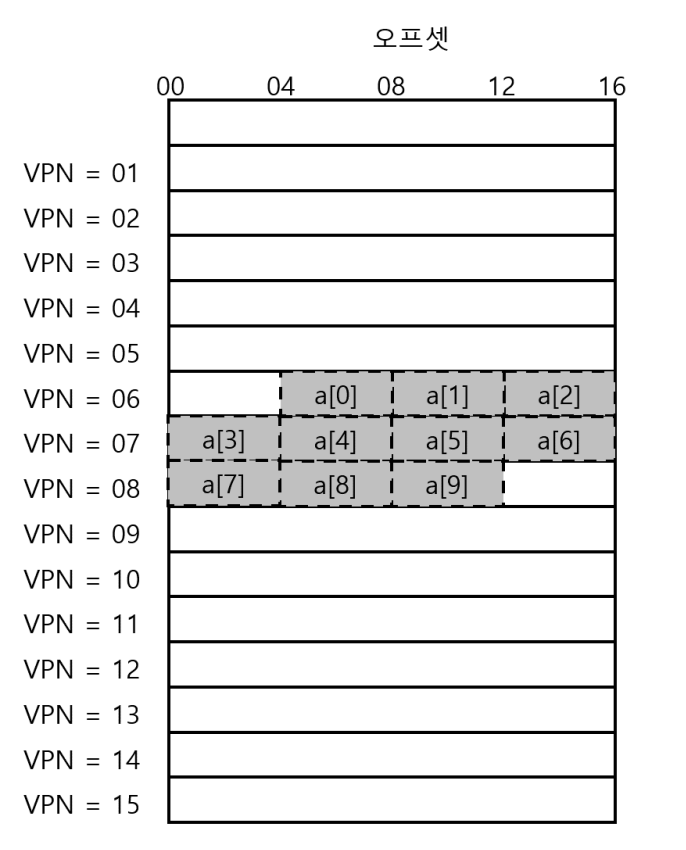

최초 a[0]에 접근하기 위해 TLB에서 VPN을 확인하면 정보가 없기 때문에 TLB miss가 일어나고 TLB정보 갱신이 일어난다. a[1], a[2]의 경우에는 공간 지역성으로 인해 TLB hit가 일어나게 된다. 만약 페이지의 크기가 더 크다면 TLB의 효과가 더 증가 할 것이다.

공간 지역성(spatial locality)

시간 지역성(temporal locality)